半導体デバイスのシャロートレンチアイソレーション(英: Shallow trench isolation)またはSTIとは、隣接する素子間でのリーク電流を防ぎ、耐圧を確保するための集積回路の素子分離構造の一つ。ボックスアイソレーションテクニック(英: box isolation technique)とも呼ばれる。 STIは一般的にテクノロジーノード250ナノメートル以下のCMOSプロセスで用いられる。 それ以前のCMOSテクノロジーやnon-MOSテクノロジーでは、一般的にLOCOSに基づく素子分離構造を用いる。

一部の半導体製造テクノロジーではディープトレンチアイソレーションも用いられ、アナログ集積回路で見られる。

トレンチエッジの効果は「逆狭チャネル効果(reverse narrow channel effect)」、または「逆狭幅効果(inverse narrow width effect)」と呼ばれる閾値電圧の変動を起こす。

端部での電界増加のため、伝導チャネル(反転層)が形成しやすくなり、閾値電圧が低下する。狭いトランジスタ幅では実効的に閾値電圧が低下する。 その結果、閾値電圧以下の伝導よりも実質大きいサブスレッショルド伝導電流が電子デバイスの問題となる。

プロセスフロー

STIが形成されるのは、トランジスタ形成より前の半導体デバイス製造プロセスの初期段階である。

- シリコン基板に絶縁膜(酸化物と保護窒化膜)を積層させる。

- リソグラフィプリント。

- ドライエッチング(反応性イオンエッチング)によってトレンチ(溝)を形成させる。このとき反応性イオンエッチングでの形状制御や、欠陥などのダメージが課題となる。

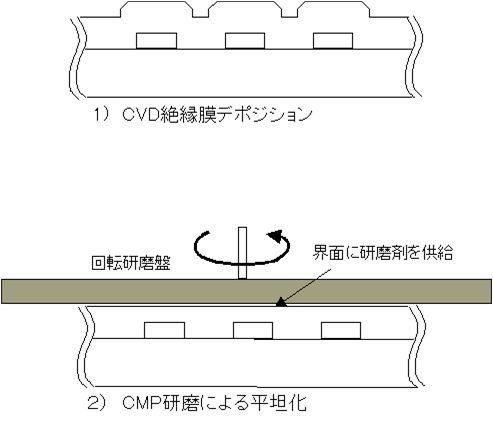

- CVDにより酸化物を堆積させ、トレンチを埋め込む。このときボイドやシームができないような埋め込み(gap fill)をする必要がある。

- 化学機械研磨(CMP)により余分な酸化物を除去し平坦化させる。このときCMPでのディッシングなどに注意が必要でする。

- 保護窒化膜を除去する

- 酸化物とSiの高さ調整をする

[1]

関連項目

- FEOL

参考文献

外部リンク

- Clarycon: Shallow trench isolation

- N and K Technologies: Shallow trench isolation

- Dow Corning: Spin on Dielectrics - Spin-on Shallow Trench Isolation